# SHARP

LCD Data Sheet

## FEATURES

- The LCD of the Unit is STHC (Super Twisted High Contrast) Gray Type

- Low Power Consumption

- Thin, Lightweight Design Permits Easy Installation in a Variety of Equipment

- General Purpose CMOS:

- The Unit can be Easily Interfaced to a Microcomputer With Common 4-Bit and 8-Bit Parallel Inputs and Outputs

- Built-in Character Generator ROM, RAM and Display Data RAM:

- Character Generator ROM 160

Different 5 × 7 Dot Matrix Character

Patterns

- Character Generator RAM Eight Different, User-Programmed 5 × 7 Dot Matrix Patterns (Write Capability by Program)

- Display Data RAM  $80 \times 8$  Bits

- Extensive Instruction Set:

- Display Clear, Cursor Home, Display ON/OFF, Cursor ON/OFF, Character Blink, Cursor Shift, and Display Shift

- Internal Automatic Reset Circuit at Power-On. Refer to the Separated Users Manual for Dot Matrix LCD Units With Built-In Controllers

- Operates From a Single 5 V Power Supply and Incorporates an LCD Panel Which Provides a Highly Stable Display Over a Wide Range of Temperatures

### DESCRIPTION

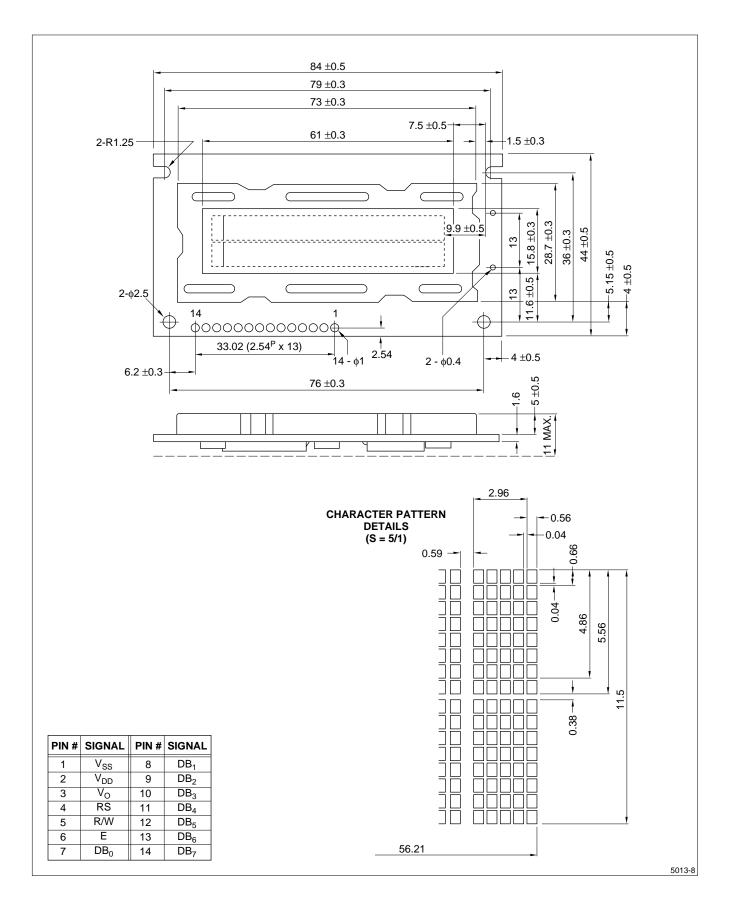

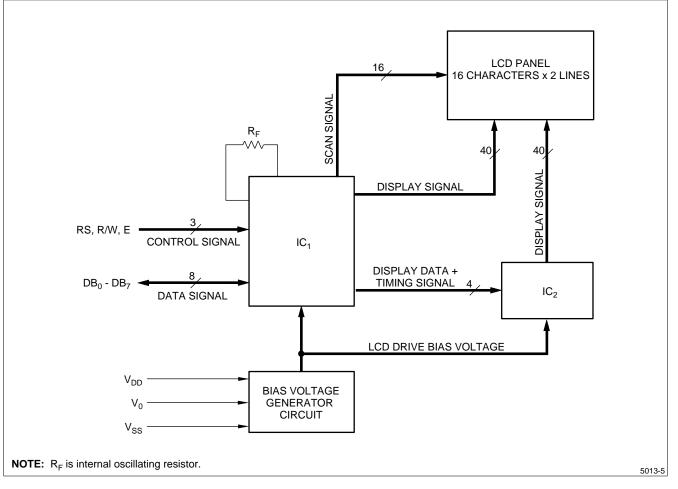

The SHARP LM16A21 Dot Matrix LCD Unit consists of a combination of a 5  $\times$  7 dot 16-character 2-line dot matrix LCD panel, LCD driver, and controller LSI mounted on a single printed circuit board. Incorporating mask ROM-based character generator and display data RAM in the controller LSI, the unit is capable of efficiently displaying the desired characters under microcomputer control.

Figure 1. LM16A21 Block Diagram

## **MECHANICAL SPECIFICATIONS**

| PARAMETER          | SPECIFICATIONS                                 | UNIT | NOTE |

|--------------------|------------------------------------------------|------|------|

| Outline Dimensions | 84 (W) $\times$ 44 (H) $\times$ 11 max (D)     | mm   | I    |

| Active Area        | 61 (W) × 15.8 (H)                              | mm   | _    |

| Display Format     | 16 characters $\times$ 2 lines                 | -    | -    |

| Character Format   | $5 \times 7$ dots, with cusor                  | -    | -    |

| Character Size     | 2.96 (W) $\times$ 4.86 (H) (5 $\times$ 7 dots) | mm   | _    |

| Dot Size           | 0.56 (W) × 0.66 (H)                            | mm   | -    |

| Dot Spacing        | 0.04                                           | mm   |      |

| Character Color    | Dark blue                                      | 1    | 1    |

| Backlight Color    | Gray                                           | -    | 1    |

| Weight             | Approximately 28                               | g    | _    |

#### NOTE:

1. Due to the characteristics of the LC material, the colors vary with environmental temperature.

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | PARAMETER                  | MIN. | MAX.                 | UNIT | NOTE        |

|-------------------|----------------------------|------|----------------------|------|-------------|

| $V_{DD} - V_{SS}$ | Supply Voltage (Logic)     | -0.3 | +6.5                 | V    | _           |

| $V_{O} - V_{SS}$  | Supply Voltage (LCD Drive) | 0    | +6.5                 | V    | $VDD > V_O$ |

| V <sub>IN</sub>   | Input Voltage              | -0.3 | V <sub>DD</sub> +0.3 | V    | _           |

| Tstg              | Storage Temperature        | -25  | +70                  | °C   | _           |

| Topr              | Operating Temperature      | 0    | +50                  | °C   | _           |

# ELECTRICAL CHARACTERISTICS ( $t_A = 25^{\circ}C$ )

| SYMBOL                   | PARAMET                         | ER      | MIN. | TYP. | MAX.     | UNIT | NOTE                         |

|--------------------------|---------------------------------|---------|------|------|----------|------|------------------------------|

| Vdd - Vss                | Supply Voltage                  | (Logic) | 4.75 | 5.0  | 5.25     | V    | _                            |

| $V_{\rm O} - V_{\rm SS}$ | Supply Voltage<br>(LCD Drive)   |         | -    | 0.5  | _        | V    | $V_{DD} = 5.0 V$             |

| V <sub>IL</sub>          | Input Voltage                   | 'L'     | -0.3 | Ι    | 0.6      | V    | —                            |

| VIH                      | input voltage                   | 'H'     | 2.2  | Ι    | $V_{DD}$ | V    | —                            |

| Vol                      | Output Voltage                  | 'L'     | _    | -    | 0.4      | V    | I <sub>OL</sub> = 1.2 mA     |

| V <sub>OH</sub>          | Output Voltage                  | 'H'     | 2.4  | Ι    | _        | V    | $I_{OH} = -0.205 \text{ mA}$ |

| IIL                      | Input Leakage C                 | urrent  | _    | 1    | 1        | μA   | _                            |

| fosc                     | Internal Oscillati<br>Frequency | ng      | _    | 250  | _        | kHz  | _                            |

| I <sub>DD</sub>          | Supply Current                  |         | _    | 1.6  | 2.2      | mA   | V <sub>DD</sub> = 5.0 V      |

| PD                       | Power Dissipation               | on      | _    | 8    | 11       | mW   | $V_0 = 0 V$                  |

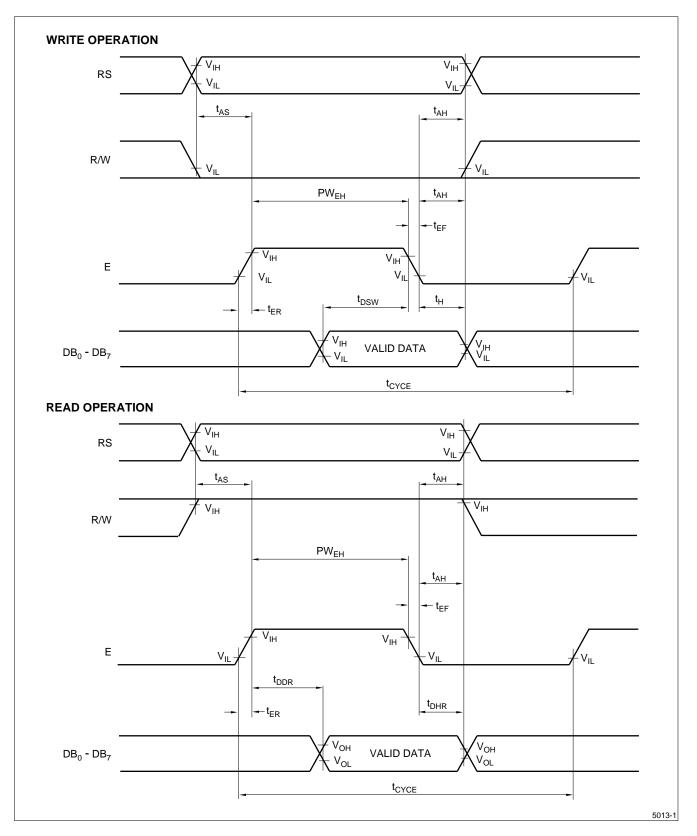

# INTERFACE TIMING (V\_{DD} = 5.0 V $\pm 5\%, \, t_A$ = 0 to 50°C)

| SYMBOL                            | PARAMETER              | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------|------------------------|------|------|------|------|

| t <sub>CYCE</sub>                 | Enable Cycle Time      | 1000 | _    | 1    | ns   |

| PW <sub>EH</sub>                  | Enable Pulse Width     | 450  | _    | -    | ns   |

| t <sub>ER</sub> , t <sub>EF</sub> | Enable Rise/Fall Time  | _    | _    | 25   | ns   |

| t <sub>AS</sub>                   | RS, R/W Setup Time     | 140  | _    | 1    | ns   |

| t <sub>AH</sub>                   | Address Hold Time      | 10   | _    | -    | ns   |

| t <sub>DSW</sub>                  | Data Setup Time        | 195  | _    |      | ns   |

| t <sub>DDR</sub>                  | Data Delay Time        | _    | _    | 320  | ns   |

| tн                                | Data Hold Time (Write) | 10   | _    | _    | ns   |

| <b>t</b> DHR                      | Data Hold Time (Read)  | 20   | _    | -    | ns   |

Figure 2. Interface Timing Chart

## **PIN CONNECTIONS**

| PIN<br>NUMBER | SYMBOL          | DESCRIPTION                 | CONNECTION                                                                                           |  |  |  |  |  |

|---------------|-----------------|-----------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1             | V <sub>SS</sub> | Ground Potential            | GND: 0 V                                                                                             |  |  |  |  |  |

| 2             | V <sub>DD</sub> | Power Supply (Logic)        | +5 V Power Supply                                                                                    |  |  |  |  |  |

| 3             | Vo              | Contrast Adjustment Voltage | Adjust the contrast by supplying voltage from 0 V to 5 V.                                            |  |  |  |  |  |

| 4             | RS              | Register Select Pin         |                                                                                                      |  |  |  |  |  |

| 5             | R/W             | Read/Write Pin              | Control signal inputs                                                                                |  |  |  |  |  |

| 6             | Е               | Enable Pin                  |                                                                                                      |  |  |  |  |  |

| 7             | DB <sub>0</sub> | Code I/O Data LSB           |                                                                                                      |  |  |  |  |  |

| 8             | DB <sub>1</sub> | Code I/O Data 2nd Bit       |                                                                                                      |  |  |  |  |  |

| 9             | DB <sub>2</sub> | Code I/O Data 3rd Bit       | <ul> <li>Data bus signals</li> <li>DB<sub>7</sub> may also be used to check the busy flag</li> </ul> |  |  |  |  |  |

| 10            | DB <sub>3</sub> | Code I/O Data 4th Bit       | <ul> <li>Lines DB<sub>0</sub> - DB<sub>3</sub> are not used when</li> </ul>                          |  |  |  |  |  |

| 11            | DB <sub>4</sub> | Code I/O Data 5th Bit       | interfacing with a 4-bit microprocessor                                                              |  |  |  |  |  |

| 12            | DB <sub>5</sub> | Code I/O Data 6th Bit       |                                                                                                      |  |  |  |  |  |

| 13            | DB <sub>6</sub> | Code I/O Data 7th Bit       |                                                                                                      |  |  |  |  |  |

| 14            | DB7             | Code I/O Data MSB           |                                                                                                      |  |  |  |  |  |

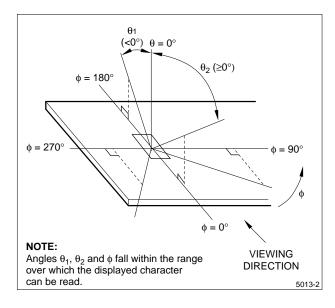

# **OPTICAL CHARACTERISTICS** ( $V_{DD} - V_O = 4.0 V$ , $t_A = 25^{\circ}C$ )

| SYMBOL                                  | PARAMETER              | CONE                                    | DITION                      | MIN. | TYP. | MAX. | UNIT    | NOTE |

|-----------------------------------------|------------------------|-----------------------------------------|-----------------------------|------|------|------|---------|------|

| $\mathbf{\theta}_2 - \mathbf{\theta}_1$ |                        | $\phi = 0^{\circ}$                      | C <sub>0</sub> ≥ 2.0        | 60   | _    | _    |         |      |

| <b>θ</b> 1                              |                        |                                         | C <sub>0</sub> = 2.0        | _    | _    | -25  |         |      |

| <b>θ</b> 2                              | Viewing Angle Range    | $\mathbf{\theta}_1 < \mathbf{\theta}_2$ |                             | 25   | _    | _    | degrees | 1    |

| $\mathbf{\theta}_2 - \mathbf{\theta}_1$ |                        | φ = 45°                                 | C <sub>0</sub> ≥ 2.0        | 60   | _    | _    |         |      |

| <b>θ</b> 1                              |                        | ່ 315°                                  | C <sub>0</sub> = 2.0        | -    | -    | -25  |         |      |

| θ <sub>2</sub>                          |                        | $\mathbf{\theta}_1 < \mathbf{\theta}_2$ |                             | 25   | _    | _    |         |      |

| C <sub>0</sub>                          | Contrast Ratio         | $\mathbf{\Theta} = 0^{\circ}$           | $\phi = 0^{\circ}$          | 3.0  | 5.0  | _    | _       | 2    |

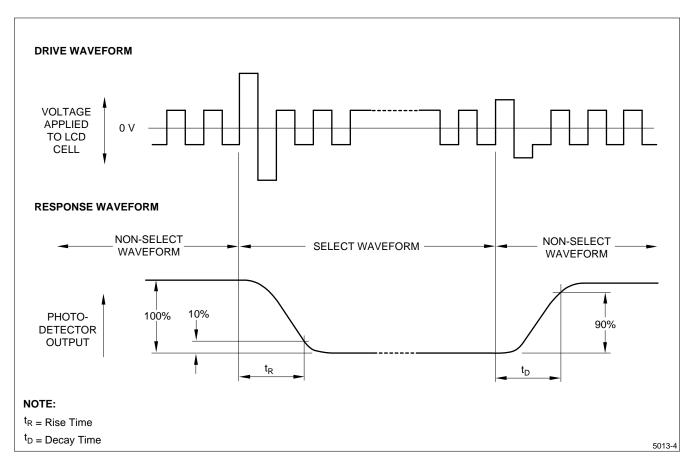

| t <sub>R</sub>                          | Response Speed – Rise  | $\mathbf{\Theta} = 0^{\circ},$          | $\mathbf{\phi} = 0^{\circ}$ | _    | 150  | 250  | ms      | 3    |

| t <sub>D</sub>                          | Response Speed – Decay | $\mathbf{\Theta}=0^{\circ},$            | $\mathbf{\phi} = 0^{\circ}$ | _    | 150  | 250  | ms      | 3    |

#### NOTES:

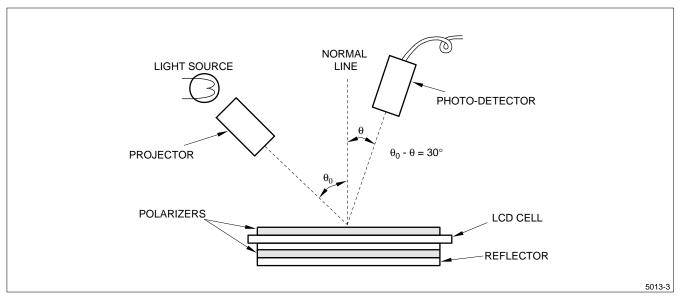

- 1. The viewing angle range may be defined as shown in Figure 3.

- 2. Contrast ratio is defined as follows:

- When input signal is applied to the unit to select (turn on) the LCD dots (pixels) to be measured in the optical characteristics test method as defined in Figure 4.

Contrast ratio =  $\frac{Photodetector output voltage with non-select waveform being applied}{Photodetector output voltage with non-select waveform being applied}$

$\frac{1}{1} \frac{1}{1} \frac{1}$

3. When input signal for selecting or non-selecting the dots to be measured are applied using the optical characteristics test method shown in Figure 4. The response characteristics of the photodetector output are measured as shown in Figure 5.

Figure 3. Definition of Viewing Angle

Figure 4. Optical Characteristics Test Method

Figure 5. Definition of Response Time

#### **PIN DESCRIPTION**

#### VDD and VSS Pins

$V_{\text{DD}}$  and  $V_{\text{SS}}$  pins are for power supply.  $V_{\text{SS}}$  pin is grounded, and  $V_{\text{DD}}$  pin is supplied with +5 V. The voltage necessary to drive the LCD is generated in the unit.

#### **RS** Pin

The controller LSI contains two 8-bit registers: instructions register (IR) and data register (DR).

RS pin selects these registers. IR serves to store instruction codes for display clear, shift, etc. and address information for display data RAM (DD RAM), character generator RAM (CG RAM); DR serves to temporarily store data to be written into DD RAM and CG RAM.

- '0': Instruction register (Write)Busy flag register; address counter (Read)

- '1': Data register (Read/Write)

#### R/W Pin

Read or write selection signal pin.

'0': Write

'1': Read

#### E Pin

Data read or write operation enable signal pin.

#### DB<sub>0</sub> to DB<sub>7</sub> Pins

Tri-state bidirectional data bus pins. The bus allows data to be transmitted to or received from the external circuit.  $DB_7$  serves also as busy flag output. When the unit is interfaced to a microcomputer with 4-bit parallel outputs,  $DB_0$  to  $DB_3$  pins are not used.

#### Vo Pin

Viewing angle is varied and contrast is adjusted by changing input voltage between +5 V to 0 V by applying bias voltage to the LCD driver.

### **INSTRUCTION SET**

| INSTRUCTION                           | CODES |     |     |           |                   |        |        |                 | DESCRIPTION     |                 |                                                                                                                   |  |

|---------------------------------------|-------|-----|-----|-----------|-------------------|--------|--------|-----------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------------|--|

| INSTRUCTION                           | RS    | R/W | DB7 | $DB_6$    | $DB_5$            | $DB_4$ | $DB_3$ | DB <sub>2</sub> | DB <sub>1</sub> | DB <sub>0</sub> | DESCRIPTION                                                                                                       |  |

| Display Clear                         | 0     | 0   | 0   | 0         | 0                 | 0      | 0      | 0               | 0               | 1               | Clears entire display area, restores display<br>from shift, and loads address counter with DD<br>RAM address 00H. |  |

| Display/Cursor<br>Home                | 0     | 0   | 0   | 0         | 0                 | 0      | 0      | 0               | 1               | *               | Restores display from shift and loads address counter with DD RAM address 00 <sub>H</sub> .                       |  |

| Entry Mode<br>Set                     | 0     | 0   | 0   | 0         | 0                 | 0      | 0      | 1               | I/D             | S               | Specifies cursor advance direction and displays shift mode. This operation takes place after each data transfer.  |  |

| Display<br>ON/OFF                     | 0     | 0   | 0   | 0         | 0                 | 0      | 1      | D               | С               | В               | Specifies activation of display (D), cursor (C),<br>and blinking of character at cursor position (B).             |  |

| Cursor/<br>Display Shift              | 0     | 0   | 0   | 0         | 0                 | 1      | S/C    | R/L             | *               | *               | Shifts display or move cursor.                                                                                    |  |

| Function Set                          | 0     | 0   | 0   | 0         | 1                 | DL     | 1      | 0               | *               | *               | Sets interface data length (DL).                                                                                  |  |

| CG RAM<br>Address Set                 | 0     | 0   | 0   | 1         | 1 A <sub>CG</sub> |        |        |                 |                 |                 | Loads the address counter with CG RAM address. Subsequent data is CG RAM data.                                    |  |

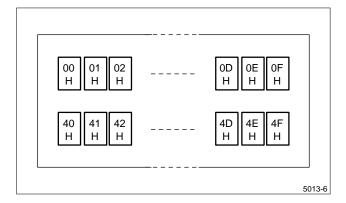

| DD RAM<br>Address Set                 | 0     | 0   | 1   |           |                   |        | Add    |                 |                 |                 | Loads the address counter with a DD RAM address. Subsequent data is DD RAM DATA.                                  |  |

| Busy Flag/<br>Address<br>Counter Read | 0     | 1   | BF  |           | A <sub>C</sub>    |        |        |                 |                 |                 | Reads out busy flag (BF) and contents of address counter ( $A_C$ ).                                               |  |

| CG RAM/<br>DD RAM Data<br>Write       | 1     | 0   |     |           |                   | Write  | e data |                 |                 |                 | Writes data into DD RAM or CG RAM.                                                                                |  |

| CG RAM/<br>DD RAM Data<br>Read        | 1     | 1   |     | Read data |                   |        |        |                 |                 |                 | Reads data from DD RAM or CG RAM.                                                                                 |  |

#### NOTES:

- I/D = 1: Increment

- S = 1: Display shift

- D = 1: Display ON

- C = 1: Cursor ON

- B = 1: Character at cursor position blinks

- I/D = 0: Decrement

- S = 0: Display freeze

- D = 0: Display OFF

- C = 0: Cursor OFF

Figure 6. Display Address (When the Display is Not Shifted)

- B = 0: Character ar cursor position unblinks

- S/C = 1: Display shift

- R/L = 1: Right shift

- DL = 1: 8 bits

- BF = 1: During internal operation

- S/C = 0: Internal cursor shift

- R/L = 0: Left shift

- DL = 0: 4 bits

- BF = 0: End of internal operation

| HIGH-ORDER          |                  |      |           |             |    |             |          |             |             |          |      |      |      |

|---------------------|------------------|------|-----------|-------------|----|-------------|----------|-------------|-------------|----------|------|------|------|

| LOW-<br>ORDER 4 BIT | 0000             | 0010 | 0011      | 0100        |    | 0110        | 0111     | 1010        | 1011        | 1100     | 1101 | 1110 | 1111 |

| xxxx0000            | CG<br>RAM<br>(1) |      |           |             |    | ••          | <b>.</b> |             |             | ••••     | •••• |      | *    |

| xxxx0001            | (2)              | -    |           |             |    |             | •        |             |             |          |      | •    | *    |

| xxxx0010            | (3)              |      | •         |             |    |             | ]<br>]   |             | ·           |          | 23   | *    |      |

| xxxx0011            | (4)              |      |           |             | :  | ŧ•          | •••••    |             |             | •••••    |      | €.   | ##   |

| xxxx0100            | (5)              |      |           |             |    |             | ÷.       | •.          |             |          | 1.1  | *    |      |

| xxx0101             | (6)              |      | •••••     |             |    | •           | <b>.</b> | ##          | •••         | •        |      |      |      |

| xxx0110             | (7)              |      |           |             |    |             | ١.,١     |             |             | ••••     |      | *    |      |

| xxxx0111            | (8)              |      | ••••<br>• |             |    | •           |          |             | •••••       |          |      | *    |      |

| xxxx1000            | (1)              | ŝ.   |           | <b>.</b>    | 24 | ŀ"1         | 24       | -: <b>!</b> | •           | •••••••• |      |      |      |

| xxxx1001            | (2)              |      |           |             |    |             | ••••     | *           |             |          |      | 1    | *    |

| xxxx1010            | (3)              | :    | ##        |             |    | •           |          |             |             | 1        | 1.~  | *    |      |

| xxxx1011            | (4)              |      | #<br>•    | Þ.          |    |             |          | <b>;:</b> † |             |          |      | ::   |      |

| xxxx1100            | (5)              |      | •         |             |    |             |          | 12          |             | ••••     |      | ÷.   |      |

| xxxx1101            | (6)              |      |           |             |    | <b>F</b> *1 |          |             | ••••<br>••• | ••••     |      |      | •    |

| xxxx1110            | (7)              | ==   |           | <b>P.</b> ] |    | <b>!</b>    | •••••    |             |             |          | •••  |      |      |

| xxxx1111            | (8)              | •*   |           |             |    |             | 4        | • ; ;       | ۰.<br>      | •••      |      |      | *    |

#### NOTES:

CG RAM is character generator RAM in which user-definable character patterns are stored.

X mark: prohibition of input.

Figure 7. Input Code Vs. Charater Pattern